Single Color Camera FPGA Architecture¶

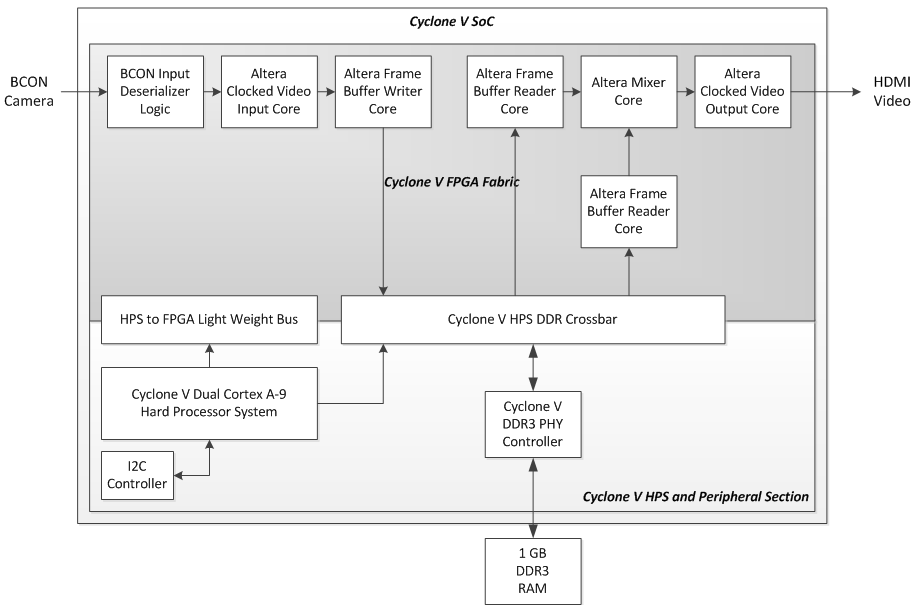

For the single camera configurations, a simple FPGA video pipeline is implemented in the FPGA according to the figure shown below:

The FPGA register memory map is defined in the following table:

| Core | Name | Base Address |

|---|---|---|

| System ID Peripheral | sysid_qsys | 0x0xFF200000 |

| Altera PIO | ugpio | 0x0xFF201000 |

| Frame Buffer II (Reader Only) - Overlay Graphics | overlay_rd | 0x0xFF202000 |

| Mixer II | mixer | 0x0xFF203000 |

| Clocked Video Output II | cvo | 0x0xFF204000 |

| bcon_input - BCON Deserializer | cam1_input | 0x0xFF205000 |

| Altera PLL Reconfig | cam1_pll_reconfig | 0x0xFF206000 |

| Frame Buffer II (Writer Only) - Frame Data In | cam1_wr | 0x0xFF207000 |

| Frame Buffer II (Reader Only) - Frame Data Out | cam1_rd | 0x0xFF208000 |

Go to top