Pin connection

Added by Mohammad Hassan Adeli 5 months ago

Hello,

I have a development kit of MitySOM-5csx (https://www.criticallink.com/product/mitysom-5csx-dev-kit/). I was wondering can anyone let me know where the Y13 pin of the FPGA module is connected internally in this board.

Thanks,

Hassan

Replies (5)

RE: Pin connection - Added by Michael Williamson 5 months ago

Hi Mohammad,

If you open up the Datasheet and check Table 8 and search for Y13 you should that it is a direct connect to the EDGE connector (I believe pin 117, but you should double check).

There is no other connection.

With regards,

Mike

RE: Pin connection - Added by Mohammad Hassan Adeli 5 months ago

Thanks for your reply, Mike. I used Y13 as the clock pin in the development board and I wonder where internally in the layout of the development kit it is connected.

I want to remove just the FPGA module and use it alone in my project and want to know what should I provide to this PIN 117 externally in the schematic so that it can be worked separately.

Thanks,

RE: Pin connection - Added by Daniel Vincelette 5 months ago

Hello Mohammad,

Please take a look at our development board schematic, if you haven't already. It can be found here: https://support.criticallink.com/redmine/projects/5csxbase/wiki/Errata_and_Product_Change_Notifications. 80-000578RC-11A is the latest version of the Development Board.

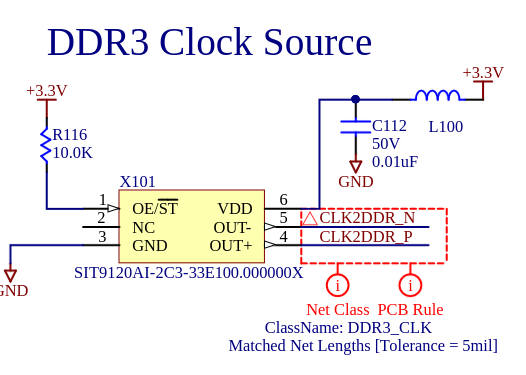

The development kit has a differential clock (X101) that drives pins 117 & 119 of the edge connector:

Best regards,

Dan

| picture280-1.png (51.2 KB) picture280-1.png |

RE: Pin connection - Added by Mohammad Hassan Adeli 5 months ago

Hello Dan,

Thanks for providing this information and support. According to this datasheet, the FPGA module has an external oscillator. I was wondering if there is any way to enable the internal oscillators to be used because I tried and they did not work as clock and I faced "waiting for clock" status in the signal tap analyzer.

Thanks,

Mohammad

RE: Pin connection - Added by Daniel Vincelette 5 months ago

Hi Mohammad,

You could route a clock from the HPS to the fabric, which is done through the HPS block in qsys. This clock is generated from the on SOM 25Mhz oscillator and is PLLed up to 100Mhz by the HPS. The checkbox is called "Enable HPS-to-FPGA user 0 clock" on the HPS Clocks->Output Clocks tab of the Arria_v/Cyclone Hard Processor System block in your qsys to enable it. Our reference FPGA design has this enabled.

Please note that you will need to rebuild the preloader and u-boot if you enable this clock for it to work. Also you will need to have the SOM at least boot to u-boot for the clock to be enabled.

Dan