Power Supply and Heat Dissipation¶

THIS IS A WORK IN PROGRESS

This wiki page provides some basic information about the thermal performance of the MitySBC-A5 (revision 1, with engineering silicon). It will capture some basic scenarios and document various power draw and thermal measurements made in the test.

Summary¶

| Scen | Heatsink | Ext Airlow | Amb. Temp | A5 Temp | A5 Rise | Core Cur (1) | Input Volt | Input Cur | Input Pow | Notes |

|---|---|---|---|---|---|---|---|---|---|---|

| 2 | None | N | 24 C | 12 v | ||||||

| 2 | None | Y | 24 C | |||||||

| 2 | Sink W/Fan Off | N | 25 C | 12 V | ||||||

| 3 | Sink W/Fan Off | N | 24 C | 44.25 C | 20.25 C | 12 V | 0.97 A | 11.64 W | FAN was disabled. | |

| 3 | Sink W/Fan On | N | 24 C | 29.50 C | 5.5 C | 12 V | 0.99 A | 11.88 W | 45% Duty on FAN PWM |

Additional Notes

Thermal options¶

No Heatsink, Passive Airflow¶

No Heatsink, Forced Airflow¶

Passive heatsink, Passive Airflow¶

Passive heatsink, Forced Airflow¶

Active heatsink with integrated fan¶

Load Scenarios¶

Scenario 1: Booted to Uboot¶

Scenario 2: Boot to linux¶

In this scenario, the base_project is loaded into the FPGA bitstream and the processor allowed to boot to linux and essentially run IDLE while connected to the network. The board was allowed to run for at least 20 minutes before checking the temperature.

Scenario 3: Camera ISP Pipeline Demo¶

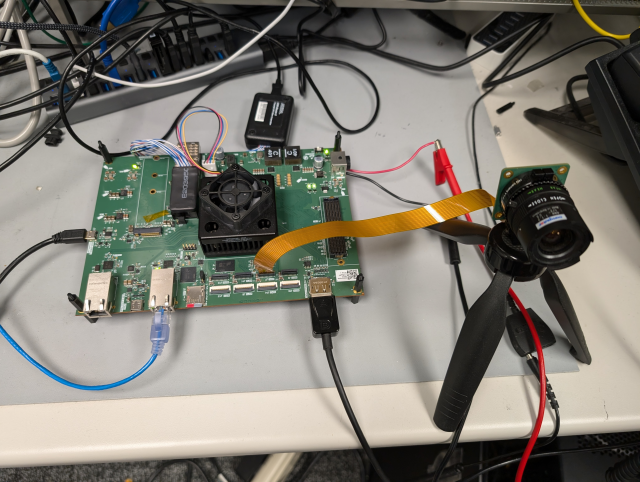

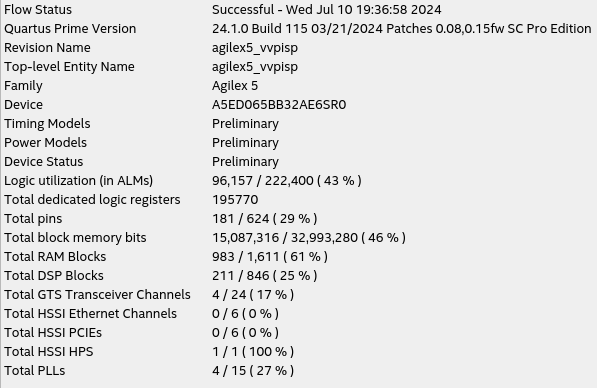

In this scenario, the Altera camera Image Signal Processing demo was run. This demo interfaces with a Raspberry PI HQ (12 MP, 12 bit) on Camera Port 0 and displays the processed output on a 30 Hz 4K DisplayPort output. It exercises some amount of the FPGA Programmable Logic core fabric with the ISP as listed in the fitter port shown below:

Go to top