HPS Peripherals¶

Bank7A Peripherals¶

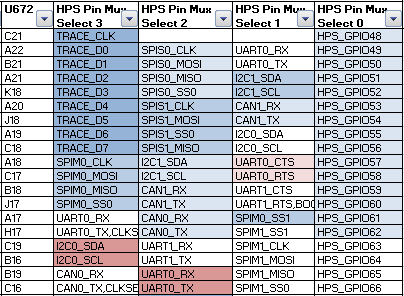

Below is a table of the peripherals in Bank7A that can be exposed through the dedicated HPS pins:

UART0 is for the default Serial Console location and has optional flow control.

I2C0 is used local to the module for the RTC and EEPROM.

UART1 will need to be routed through the FPGA fabric if desired.

Go to top