SOM_62P Reset on LED_RTN

Added by Adrian De Vico 5 months ago

We have a series of switchable LEDs on board for basic debugging of various on-board supplies, and for completeness I've included the ability to sink current from LED_RTN (pin 2 on SOM) to get some visual output from the SOM.

In terms of circuitry there is a simple FET driven from a buffer tied to a GPIO. ( GPIO -> Buffer -> { Gate resistor -> NFET Gate } x 9 in highly simplified terms)

With reference to the Critical Link development board this represents a replacement of R124 with a small transistor.

When the switching event occurs the SOM fully resets (RESETSTATz pulses low, SOM reboots), this was observed in 100% of tests. Off-SOM circuitry works as intended and with the LED_RTN FET removed the system works as intended in 100% of tests.

I'm curious if this has been observed elsewhere or has some workaround?

With time I will play with further limiting the edge rates to something arbitrarily slow, at this time I've disabled the feature as it has no major impact on any function.

Attached is a screen capture of the GPIO output showing the pin reaching a high logic level (1.8V in this case), followed quickly by the SOM resetting.

This is a low priority item for us, however I'm curious if there are any obvious reasons why this would happen.

| FailureGPIO.png (84.5 KB) FailureGPIO.png | Seen here is a GPIO driving high, immediately followed by SOM reset |

Replies (3)

RE: SOM_62P Reset on LED_RTN - Added by Michael Williamson 5 months ago

Hi Adrian,

Haven't seen this before.

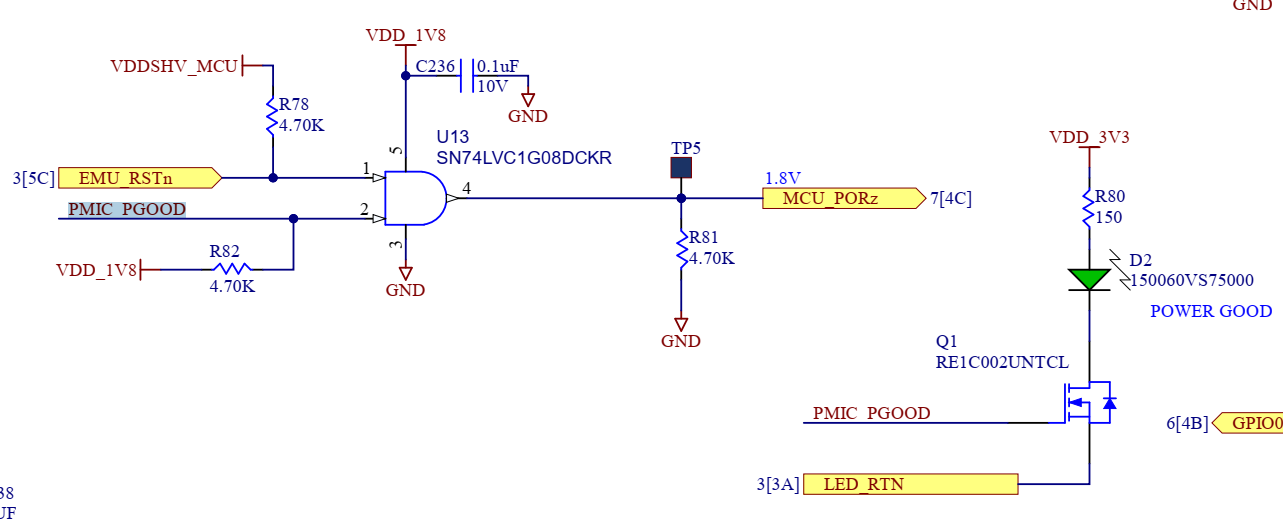

This is a snippet from the SOM schematic related to the Power Good LED and the LED_RTN Net:

As you can see, the PMIC_PGOOD is AND-ed into the main MCU_PORz. It is an open-drain output from the PMIC pulled to 1.8V via 4.7K and is also used to drive the FET. It would seem that the FET switching on your board must be perturbating the PMIC_PGOOD at the gate of Q1 and and causing the MUC_PORz to be driven low, based on your description. Looking at the schematic, we probably should have added a resistor at the input to the gate on Q1 in the design (the gate capacitance is probably passing the switch of your FET into the gate signal / bouncing PMIC_PGOOD).

Not sure if there is an easy workaround without modifying the SOM (which, if we have to spin it in the future, I will definitely add). We haven't had anyone try to actively switch that return line. We mostly put it there because we have some customers that don't want to bleed the power from the Power Good resistor during operation (in sleep mode).

-Mike

| SOM_LED_PGOOD.png (93 KB) SOM_LED_PGOOD.png |

RE: SOM_62P Reset on LED_RTN - Added by Adrian De Vico 5 months ago

That explanations seems probable, if I have any free time coming up I'll play around with the circuit on our side to get it working reliably.

For the time being we'll continue to not switch LED_RTN.

Thanks for the rapid reply!

RE: SOM_62P Reset on LED_RTN - Added by Michael Williamson 5 months ago

Wondering if you could add a LPF filter (cap + R) across your FET to make the switch less aggressive. Kind of hacky, but it might work.