- Table of contents

- Power Supply and Heat Dissipation

- Power Reduction by Disabling Interfaces

Power Supply and Heat Dissipation¶

Customers using the MitySOM-57XX SOM must be conscious of both the power supply requirements and the thermal management solution of their final design.

Test Measurements¶

Temperature and Power Data has been collected under a few different scenarios.

Thermocouples were attached to the top of the PMIC case, 1 DDR3 RAM chip case, and the top of the Artix 15 KLE FPGA case. One thermocouple was used to measure ambient air temperature. Ambient was essentially 25 C for the duration of the testing.

Temperature for the CPU, GPU, and CORE dies were captured using the onboard AM572x temperature sensors via sysfs access.

Power for the SOM was measured using the LTC2945 current monitor on the +5V input supply. Power for the Development Kit + SOM was measured using the current / power monitor available on a local RIGOL DP832 power supply used to provide +12VDC to the Development Kit.

In all tests, the CPU governor was set to ondemand with 1000, 1175, and 1500 MHz as available CPU clock options. The DSP clock rate was set to 750 MHz, the and GPU clock set to 425 MHz.

MitySOM-5728 DevKit with Stock CPU FAN¶

For this set of testing, a stock revision -2 MitySOM-57xx DevKit board and a MitySOM model 5728-PJ-4AA-RI module was evaluated using the provided CPU controller FAN attached to the AM5728 using the dual sided adhesive provided with the CPU FAN. Results are shown in the table below.

It was noted that for all the testing the CPU FAN was running at full speed.

| Scenario | SOM Power (W) | DevKit+SOM Power (W) | FPGA Rise (C) | DRAM Rise (C) | PMIC Rise (C) | CPU Rise (C) | GPU Rise (C) | Core Rise (C) | CPU 0 Load | CPU 1 Load | Test Duration (S) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| OS IDLE | 5.7 | 9.5 | 22.6 | 19.14 | 32.1 | 30 | 30 | 28 | 1 | 1 | 0 |

| Dual DhryStone | 11.2 | 15.4 | 30 | 28.6 | 47 | 59.6 | 52 | 53 | 100 | 100 | 131 |

| MemTest (RD/WR) | 9.9 | 14.1 | 24.9 | 24.8 | 37 | 45 | 42 | 43 | 100 | 100 | 48 |

| MemTest (COPY) | 10.6 | 15.1 | 28.6 | 28.1 | 42.2 | 50.4 | 47.2 | 47.6 | 100 | 100 | 47 |

| FFT (DSP Load) | 9.4 | 12.8 | 27.3 | 24.8 | 39.5 | 47.6 | 43.2 | 44 | 100 | 4 | 1971 |

| IPERF | 9.2 | 12.8 | 24.5 | 20.8 | 32.6 | 42.8 | 39.6 | 40.8 | 100 | 20 | 60 |

| Chameleon | 6.6 | 10.1 | 23.5 | 20.8 | 32.6 | 35.2 | 33.5 | 34.8 | 5 | 2 | 335 |

| FPGA -> DDR > ENET | 9.6 | 13.2 | 28.3 | 25.1 | 38.8 | 48 | 44 | 45.6 | 97 | 50 | 1328 |

A picture of the test setup is shown below.

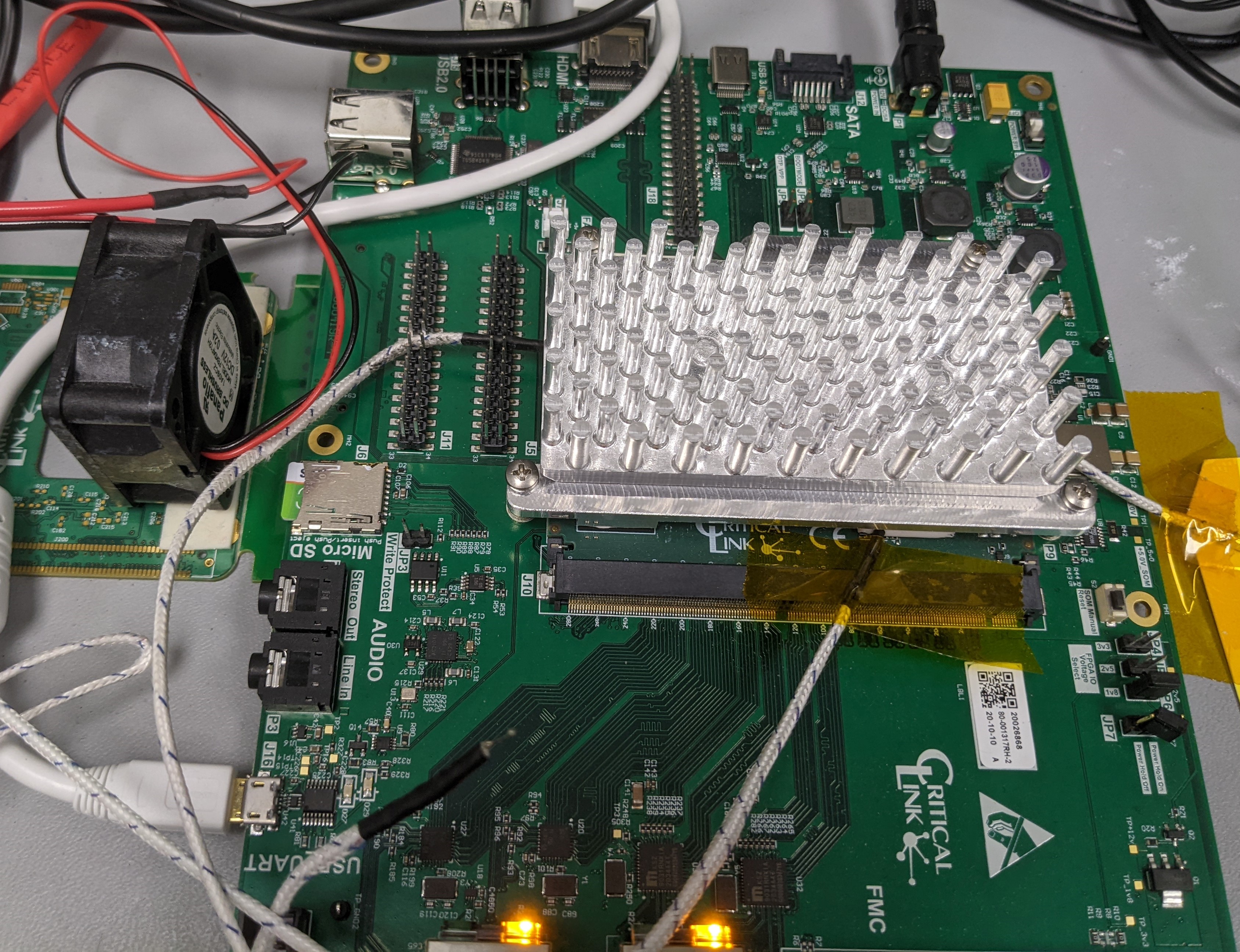

MitySOM-5728 DevKit with aluminum heat spreader, attached heat sink and forced air¶

To represent an ideal heat exchange situation, the reference heat spreader and aluminum heatsink was attached to the SOM, and external forced air was applied on the assembly. The results are shown in the table.

| Scenario | SOM Power (W) | DevKit+SOM Power (W) | FPGA Rise (C) | DRAM Rise (C) | PMIC Rise (C) | CPU Rise (C) | GPU Rise (C) | Core Rise (C) | CPU 0 Load | CPU 1 Load | Test Duration (S) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| IDLE | 6.1 | 9.3 | 5.091 | 3.859 | 4.683 | 14.8 | 12.4 | 14 | 1 | 1 | 1944 |

| Dual DhryStone | 9.6 | 13.5 | 8.951 | 7.057 | 8.173 | 30.8 | 24 | 25.2 | 100 | 100 | 275 |

| MemTest (RD/WR) | 9.9 | 13.75 | 7.071 | 5.703 | 6.461 | 24 | 20.1 | 21.2 | 100 | 100 | 113 |

| MemTest (COPY) | 9.6 | 13.1 | 7.352 | 5.889 | 6.667 | 24.4 | 21.6 | 22 | 100 | 100 | 125 |

| FFT (DSP Load) | 8.2 | 11.4 | 6.464 | 4.95 | 5.928 | 22 | 18 | 18.8 | 100 | 4 | 1974 |

| IPERF | 8.33 | 11.7 | 6.824 | 5.323 | 6.312 | 21.6 | 19.2 | 18.8 | 100 | 20 | 600 |

| Chameleon | 6.7 | 9.9 | 6.731 | 5.133 | 6.048 | 16.4 | 13.6 | 14.8 | 5 | 2 | 670 |

| FPGA - PCIE - ENET | 8.4 | 11.72 | 6.822 | 5.283 | 6.232 | 23.6 | 19.2 | 19.6 | 100 | 50 | 1631 |

A picture of the test setup is shown below.

Test Scenario Description¶

- OS IDLE : MitySOM-57xx DevKit booted with stock SD-Card image and reference FPGA loaded. HDMI display, 1 ethernet port, and USB console port connected.

- Dual DhryStone : Two instances of the dhrystone benchmark were run with a repeat count of 1000000000.

- MemTest (RD/WR) : Two instances of lmbench were run. Each instance was to perform a read/write to the same address of 400 MB, repated 20 times.

bw_mem -P 2 -N 20 400M rdwr

- MemTest (COPY) : Two instances of lmbench were run. Each instance was to perform a memory copy of 200 MB, repated 20 times.

bw_mem -P 2 -N 20 200M cp

- FFT (DSP Load) : The TI FFTW 3D single precision point FFT statistics code was performed. This performed 3D FFTs of various sizes using a combination of ARM only, and DSP offloaded FFT accelerations. The genstats_csv script in the /usr/share/ti/examples/fftw/fft_3d_sp folder was executed.

- IPERF : The iperf3 command was used as a client connection to a host server.

iperf3 -c userv1 -i 5 -t 60

- Chameleon : The TI provided ChameleonMan 3D example was run at 1920x1080p resolution.

/usr/bin/SGX/demos/DRM/OGLES2ChameleonMan -qaf=20000

- FPGA -> DDR > ENET : An example application, which transfers 120 MB/sec data from the FPGA via PCIe to DDR, and the transfers from DDR to the gigabit ethernet interface, continuously, was run. (this is the MityCAM GigE for AM57XX example application).

Power Reduction by Disabling Interfaces¶

It is possible to reduce power by disabling unused interfaces. In Critical Link's testing we have found that disabling PCIe, SATA, Video Input from the FPGA, and the GPU can give about a 1W to 1.3W reduction on the 5V input into the SOM. The PCIe and Video In require disabling them in both the FPGA project and Linux Device Tree. SATA and the GPU just need to be disabled in the FPGA Project. Please see below for further details.

| SD Card Image | SoC | FPGA Size | With Fansink | Power Draw W | ARM Temp C |

|---|---|---|---|---|---|

| Base | AM5728 | 15KLE | N | 4.83 | 64.90 |

| PCIe, FPGA Frame Generator, GPU, and SATA disabled | AM5728 | 15KLE | N | 3.27 | 55.93 |

| Base | AM5728 | 15KLE | Y | 4.97 | 44.02 |

| PCIe, FPGA Frame Generator, GPU, and SATA disabled | AM5728 | 15KLE | Y | 3.33 | 39.85 |

| Base | AM5749 | 50KLE | N | 5.62 | 70.89 |

| PCIe, FPGA Frame Generator, GPU, and SATA disabled | AM5749 | 50KLE | N | 3.81 | 62.58 |

- Ambient = 27.5C

- At Linux Idle (~1% ARM usage)

- All tests were run on a bench in Critical Link's Development Kit

- For tests without fansink, no heat sink or forced air was applied over the processor/SOM

- For tests with the fansink, a fansink was only add to the processor. The fan was set to always spin at max rate

- Ondemand CPU Govenor enabled (scales between 1Ghz to 1.5Ghz)

- Different AM5728 With 15KLE SOM used for with and without Fansink

- Base SD Card Image is the Development SD card: https://support.criticallink.com/files/MityCAM-AM57x-SDK/latest/tisdk-rootfs-image-mitysom-am57x-20220323164556.rootfs.img.zip

- PCIe, GPU, and SATA disabled SD Card is the Development SD card with the following changes

- FPGA replaced with one built from GPMC only project: https://support.criticallink.com/gitweb/?p=mitysom-am57x-ref.git;a=tree;f=fpga/devkit_basic_gpio_gpmc_only;h=50028ec20a96a3a6a09a80166e24732a1545792b;hb=HEAD

- Device Tree was edited to disable:

- FPGA video simulator and corresponding VIN port of the SoC

- GPU

- PCIe Root Port

- SATA

Device Tree Diff:

--- a/arch/arm/boot/dts/am57xx-mitysom-devkit-fpga.dts

+++ b/arch/arm/boot/dts/am57xx-mitysom-devkit-fpga.dts

@@ -88,7 +88,7 @@

video_sim {

compatible = "cl,fpga-tpg-1.0";

- status = "okay";

+ status = "disabled";

gpio,video-start = <&fpga_gpio_2 34 GPIO_ACTIVE_HIGH>;

port {

fpga_sim: endpoint {

@@ -106,12 +106,37 @@

* FPGA VIN is connected to VIN4a which is port@1 on vip2

*/

&vip2 {

- status = "okay";

+ status = "disabled";

};

&vin4a {

- status = "okay";

+ status = "disabled";

vin4a_ep: endpoint {

remote-endpoint = <&fpga_sim>;

};

};

+

+

+&pcie2_phy {

+ status = "disabled";

+};

+

+&pcie1_rc {

+ status = "disabled";

+};

+

+&sata {

+ status = "disabled";

+};

+

+&gpu {

+ status = "disabled";

+};

Go to top